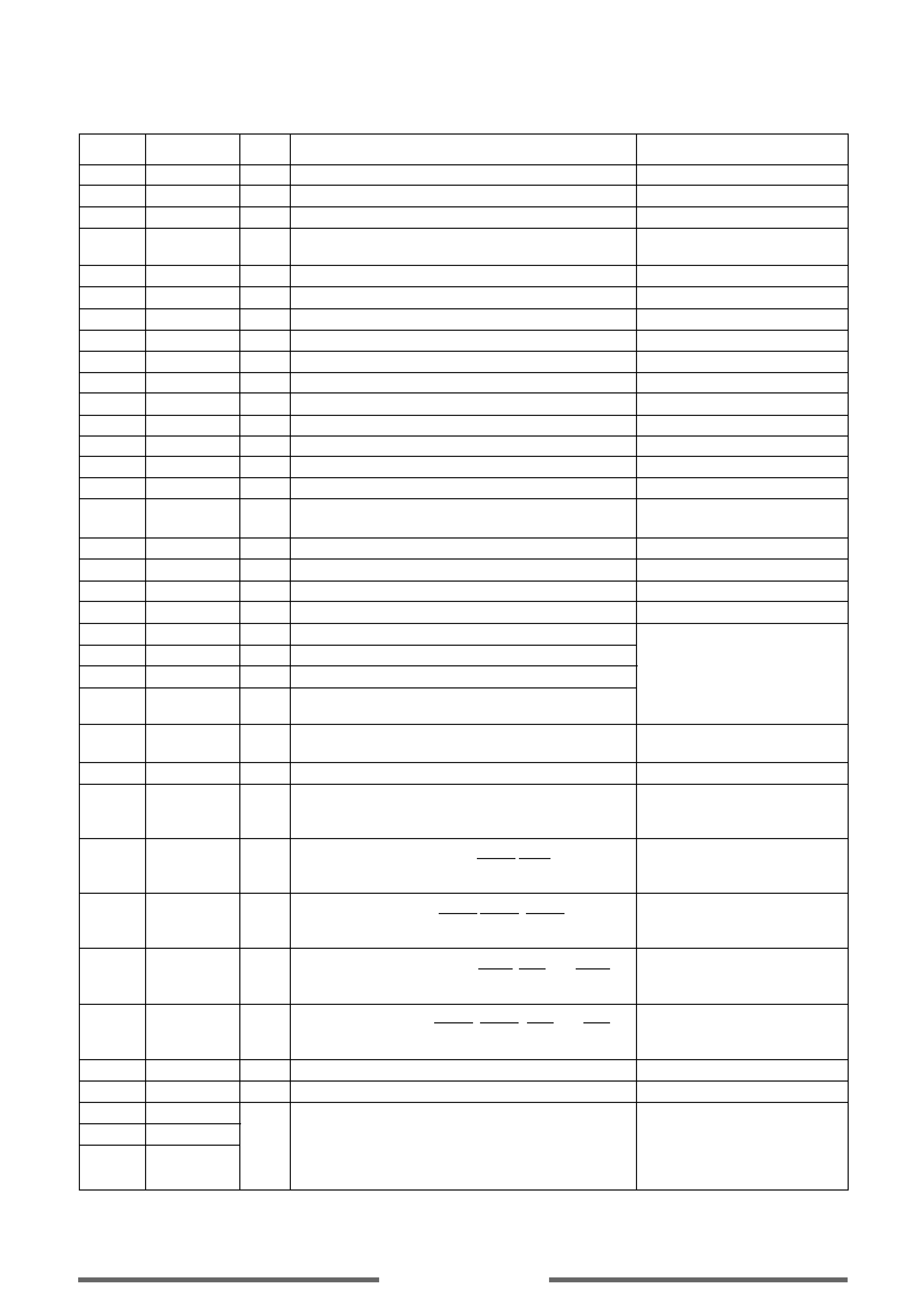

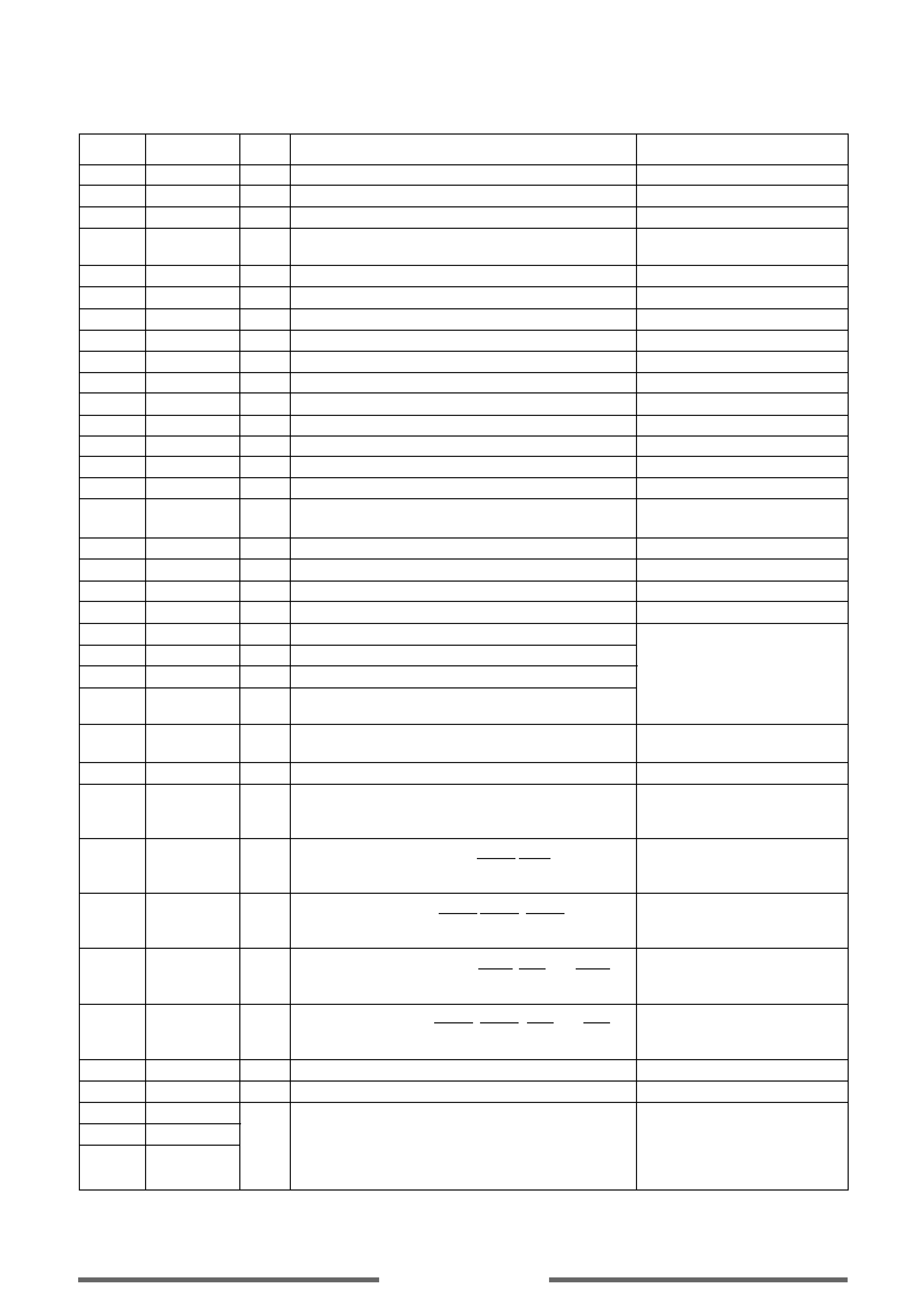

4

SERVICE MANUAL

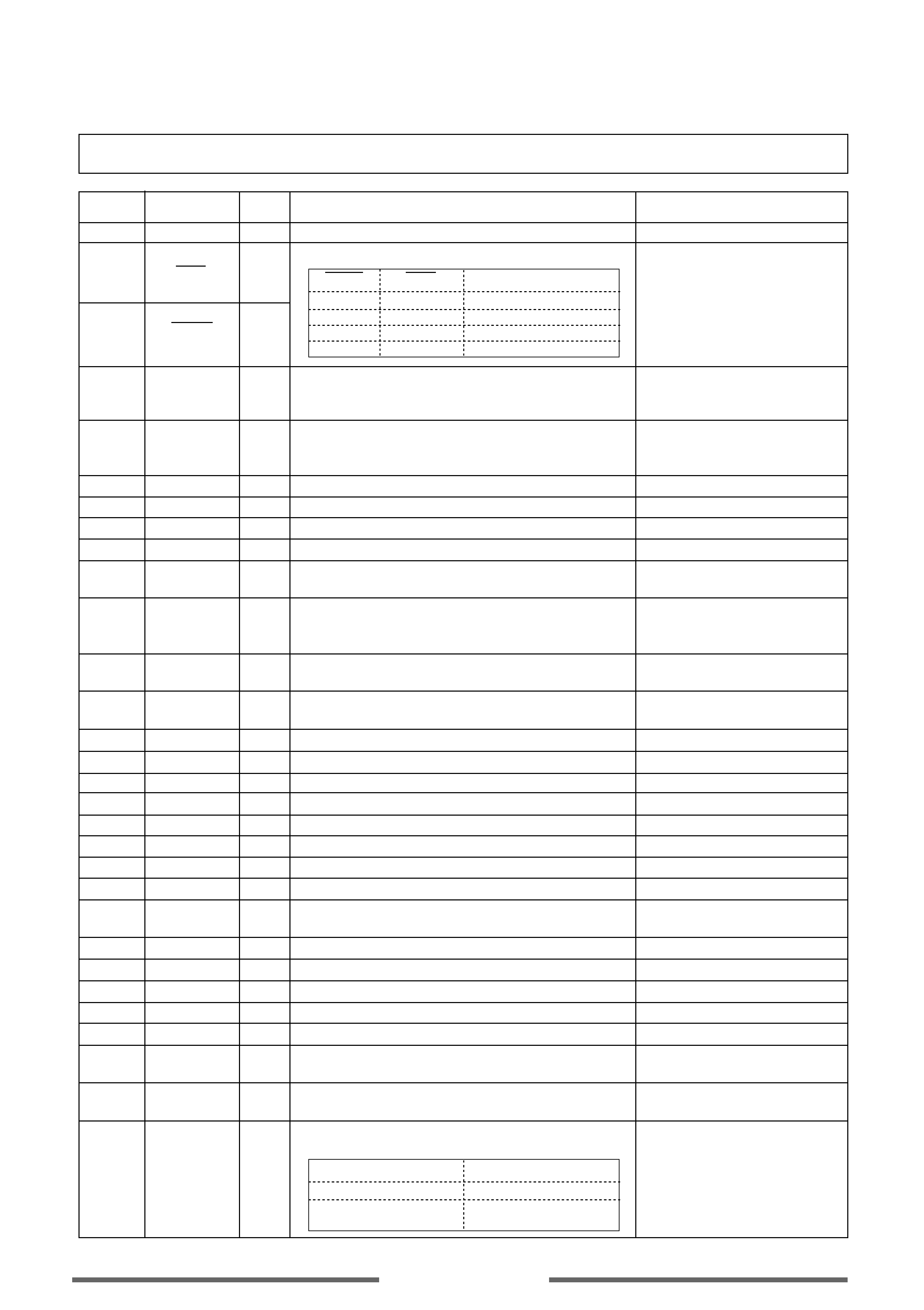

PIN No. NAME

I/O

FUNCTIONAL DESCRIPTION

REMARKS

LPFN

LPFO

PVREF

VCOREF

VCOF

AVSS

SLCO

RFI

AVDD

RFCT

RFZI

RFRP

FEI

SBAD

TSIN

TEI

TEZI

FOO

TRO

VREF

RFGC

TEBC

TEBC

TEBC

DMO

2VREF

SEL

FLGA

FLGB

FLGC

FLGD

VDD

VSS

IO0

IO1

IO2

IO3

Analog input.

Analog output.

-

-

Analog output.

-

Analog output.

Analog input (Zin : selected by command)

-

Analog input (Zin : 50k

)

Analog input.

Analog input.

Analog input.

Analog input.

Analog input.

Analog input.

Analog input (Zin : 10k

)

Analog output (2VREF~AVSS)

-

3-state PWM signal output.

(2VREF, VREF, VSS)

(PWM carrier = 88.2 kHz)

3-state PWM signal

output.(2VREF, VREF, VSS)

-

-

-

-

-

-

-

-

-

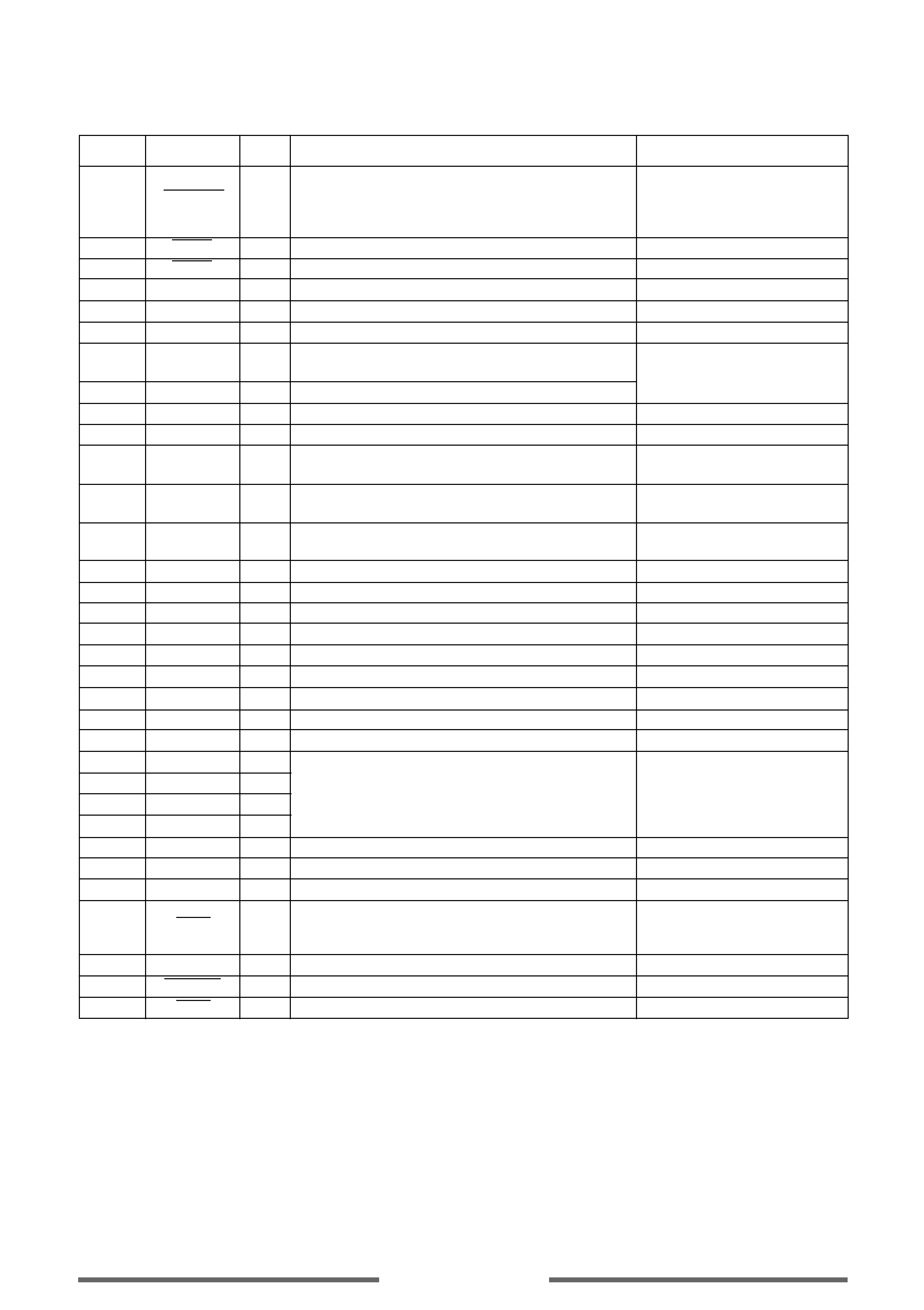

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

LPF amplifier inverting input terminal for PLL.

LPF amplifier output terminal for PLL.

PLL reference voltage supply terminal.

VCO center frequency reference level terminal.

Normally, keep at "PVREF" level.

VCO filter terminal.

Analog GND terminal.

Data slice level output terminal.

RF signal input terminal.

Analog power supply voltage terminal.

RFRP signal center level input terminal.

RFRP zero cross input terminal.

RF ripple signal input terminal.

Focus error signal input terminal.

Sub-beam adder signal input terminal.

Test input terminal. Normally, keep at "VREF" level.

Tracking error signal input terminal.

Track in at tracking servo on.

Trcaking error zero cross input terminal.

Focus servo equalizer output terminal.

Tracking servo equalizer output terminal.

Analog reference voltage supply terminal.

RF amplitude adjustment control signal output terminal.

Tracking balance control signal output terminal.

Feed equalizer output terminal.

Speed error signal or feed search equalizer output ter-

minal.

Disk equalizer output terminal. (PWM carrier = 88.2 kHz

for DSP, Synchronize to PXO)

Analog double reference voltage supply terminal.

APC circuit ON/OFF indication signal output terminal.

At the laser on time, UHF = L at "HiZ" level and

UHF = H at "H" level.

Extemal flag output terminal for internal signal.

Can select signal from TEZC, FOON, FOK and RFZC by

command.

Extemal flag output terminal for internal signal.

Can select signal from DECT, FOON, FMON and RFZC

by command.

Extemal flag output terminal for internal signal.

Can select signal from TRON, TRSR, FOK and SRCH by

command.

Extemal flag output terminal for internal signal.

Can select signal from TRON, DMON, HYS and SHC by

command.

Digital power supply voltage terminal.

Digital GND terminal.

General I/O terminal. Can change over input port or

output port by command. At the input mode time can

readout a state of terminal (H/L) by read command. At

the output mode time can control a state of terminal

(H/L/HiZ) by command.

I

O

-

I

O

-

O

I

-

I

I

I

I

I

I

I

I

O

O

-

O

O

O

O

O

-

O

O

O

O

O

-

-

I/O